安规网

标题: 强大的TYPE-C方案,简洁有效的EMC对策 [打印本页]

作者: q799232490 时间: 2017-6-28 12:29

标题: 强大的TYPE-C方案,简洁有效的EMC对策

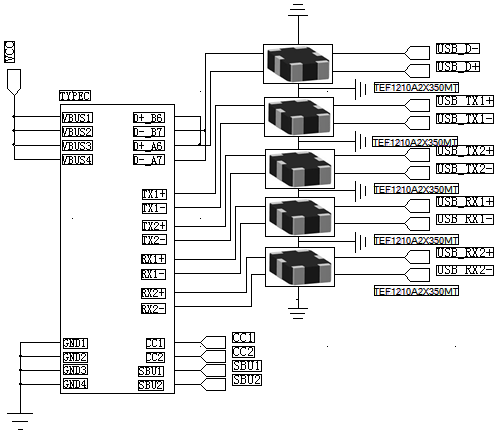

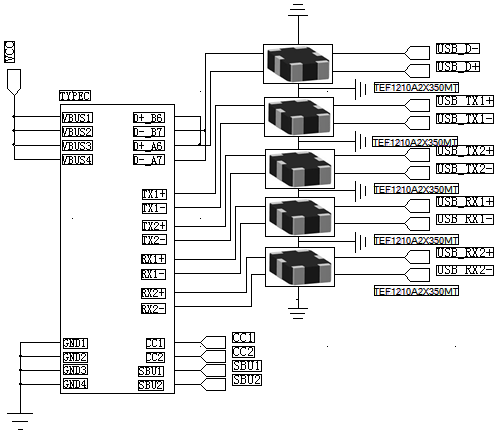

[attach]115579[/attach]

2 C; T9 _5 |9 S# R随着New MacBook的发布,支持正反插的USB TYPE-C瞬间名满全世界;随后联想、小米等知名企业纷纷推出USB TYPE-C方案的新产品,USB TYPE-C方案正式走向了新产品应用的热潮;更多精彩点这里

一、USB TYPE-C简介" `& O6 v' z* {9 s- ^ |

( [9 V. s' ]" }$ `7 a. \$ E; L6 r

+ v. t4 x( p$ }" [3 G9 `

USB TYPE-C的亮点在于更加纤薄的设计、更快的传输速度(最高10Gbps)以及更强悍的电力传输(最高100W),但是高达10GBPS的传输速度必然导致端口的辐射超标严重;而功率大、速度快特征对端口防护器件有了更高要求;如何有效、简洁的做出性价比高的方案便成了硬件工程师的难题。本文从辐射发射和抗扰度两个方面为大家提供性价比高的EMC解决方案,希望对大家有所帮助。

TYPE-C脚位定义* W$ S. D7 S) N9 u

8 s6 M; c7 i$ B0 S2 u4 H' @! b/ N[attach]115580[/attach]

! Z; {2 H" t, r3 R6 B$ k7 ~) R

2 K0 s7 |) v$ F( c- `! l3 A) I脚位说明数据传输主要有TX/RX两组差分信号,CC1和CC2是两个关键引脚,作用很多:探测连接,区分正反面,区分DFP和UFP,也就是主从配置Vbus,有USB Type-C和USB Power Delivery两种模式。配置Vconn,当线缆里有芯片的时候,一个cc传输信号,一个cc变成供电Vconn。配置其他模式,如接音频配件时,Dp,Pcie时电源和地都有4个。

/ |+ p0 t4 B u ?* P' @/ V! Z+ B

; G' X5 d" @% t- d6 M0 H! J4 ^- x0 u! T X

TYPE-C的EMC问题点: q2 O7 U* D2 G

- J! @$ q. Q7 a- j- A! x7 d; z4 L6 _6 k6 |( T6 u

9 z) y" G3 t+ D1 E4 k/ {0 O1、高达10GBPS的传输速度必然导致端口的辐射超标严重;

/ ?2 f/ {. p/ |' U# \9 }

7 j8 s7 x( i2 q$ F0 y: y4 f) w9 W" t

2、TYPE-C电压范围广、功率大、速度快特征对端口防护器件有了更高要求;

* H5 q! h* O1 X# U" Z, a# B

* {: q/ y7 s2 x! Q0 l- v+ w, K9 E! g

" j, M2 C$ E |) W- V 处理措施5 Q' g; E, C; M! z

7 M6 i: ^- V" X) S% f

8 U+ f$ T5 @" A9 a8 f2 S) s+ c0 m(一)、TYPE-C的EMI问题;

/ E3 p2 [( |9 [/ Y# E3 p

( ^ [. R0 c8 o- P! ?; P7 }问题点:高速数据交换时产生的共模辐射,例如240MHZ、480MHZ、720MHZ等;

[attach]115582[/attach]

措施:在差分线上增加43R共模滤波器;

数据对比:

[attach]115581[/attach]

* X) w+ S+ W" c# Q2 J说明:增加共模滤波器后,480MHZ下降明显;泰派斯特致力于打造电磁兼容领域的第一品牌,为国防事业保驾护航!

7 Z+ I) [/ i" Q' l; U/ x

+ W( `) P; o' w4 b* }) x9 l8 c) X3 Y9 _4 i+ m8 g- U

(二)、TYPE-C的ESD问题;+ f N7 t( N9 A3 w, c& O

`) f! o( N& P. W4 c) X

问题点:对TYPE-C端口进行静电放电时,会导致系统死机或数据交换中断;

- |) |8 a+ o5 I/ E2 I: Y( }8 b: a- T

措施:在差分线上增加0.4PF的TVS排;

- R$ |+ N# I H+ a

[attach]115577[/attach]

. q$ U# L) Z8 I" q. I

说明:在信号线上增加TVS,能有效抑制静电对系统的影响。

/ i4 |$ c# V$ _; o! X h

( t0 f! ~. }! [0 V, S; v(三)、TYPE-C的EMC问题处理;

, J/ c$ |- x( l* H

: A5 A& U6 l+ r) l2 }处理:在差分线上增加带静电防护的共模滤波器

& {. x# m+ v$ q; r$ Z7 ~; k说明:带静电防护的共模滤波器能最大限度的节省PCB的有限空间,便于优化走线,提升

EMC性能。

+ b- B' v+ m4 A: s" d- h2 @+ T( p PCB layout注意事项

j- a2 U9 J, r: q' e, ~5 C. T* u, ]3 |' U4 m

# T- D) d2 i3 }" r6 j9 P

(一)差分对走线要求1、差分线上不应加磁珠或者电容等滤波措施,否则会严重影响差分线的阻抗。

2、差分信号线要求至少紧邻一个地平面,两侧都紧邻地平面最好。

3、保持USB2.O差分线下端地层完整性,如果分割差分线下端的地层,会造成差分线阻 抗的不连续性,并会增加外部噪声对差分线的影响。

4、在差分线的布线过程中,应避免在差分线上放置过孔(via),过孔会造成差分线阻抗失调。如果必须要通过放置过孔才能完成差分线的布线,那么应尽量使用小尺寸的过孔,并保持差分线在一个信号层上。

5、保证差分线的线间距在走线过程中的一致性,差分线要尽量等长,如果两根线长度差较大时,可以绘制蛇行线增加短线长度。

6、在绘制差分线的过程中,使用45°弯角或圆弧弯角来代替90°弯角,并尽量在差分线周围的150mil范围内不要走其他的信号线,特别是边沿比较陡峭的数字信号线更加要注意其走线不能影响差分线。

0 h E/ E, A) y ?

1 u- N8 b" M4 A7 E) @

}1 Q' E$ @3 _, j. M3 \) u- H(二)在绘制电源线、信号地和保护地时,应注意以下几点:1、插座的1、2、3、4 脚应在信号地的包围范围内,而不是在保护地的包围范围内。

2、差分信号线和其他信号线在走线的时候不应与保护地层出现交叠。

& T7 R5 S& x4 @3、电源层和信号地层在覆铜的时候要注意不应与保护地层出现交叠。

8 U+ _/ l. j0 E3 g, F ]/ _) e4、电源层要比信号地层内缩20H,H为电源层与信号地层之间的距离。

6 j$ W% Z- [0 H7 h9 E5、如果差分线所在层的信号地需要大面积覆铜,注意信号地与差分线之间要保证35mil以上的间距,以免覆铜后降低差分线的阻抗。

6、在其他信号层可以放置一些具有信号地属性的过孔,增加信号地的连接性,缩短信号电流回流路径。

7、在电源线和PCB板的电源线上,可以加磁珠增加电源的抗干扰能力。

+ k7 u' q4 ~4 G0 O, W

* Q2 {9 Y# z. G" k+ U0 N, c7 z* H* `7 h3 m$ ?! a% j

作者: 弹指飞烟 时间: 2017-6-30 08:36

不明觉厉

| 欢迎光临 安规网 (http://bbs1.angui.org/) |

Powered by Discuz! X3.4 |